# Fully Depleted, Monolithic Pinned Photodiode CMOS Image Sensor Using Reverse Substrate Bias

Konstantin D. Stefanov, Andrew S. Clarke, James Ivory and Andrew D. Holland

Centre for Electronic Imaging, The Open University, Walton Hall, Milton Keynes, MK7 6AA, UK

#### Summary

A new pixel design using fully depleted pinned photodiode (PPD) in a 180 nm monolithic CMOS image sensor (CIS) process has been developed as a proof of principle. The sensor can be fully depleted by means of reverse bias applied to the substrate, and the principle of operation is applicable to very thick sensitive volumes. Additional n-type implants, called Deep Depletion Extension (DDE) under the in-pixel p-wells have been added to the manufacturing process in order to eliminate the large parasitic substrate current that would otherwise be present in a normal device. The new design exhibits nearly identical electro-optical performance under reverse bias as the reference PPD pixel it is based on, and the leakage current is effectively suppressed. The characterisation results from both front- and back-side illuminated sensor variants show that the epitaxial layer is fully depleted. This development has the potential to greatly increase the quantum efficiency of PPD CIS at near-infrared and soft X-ray wavelengths.

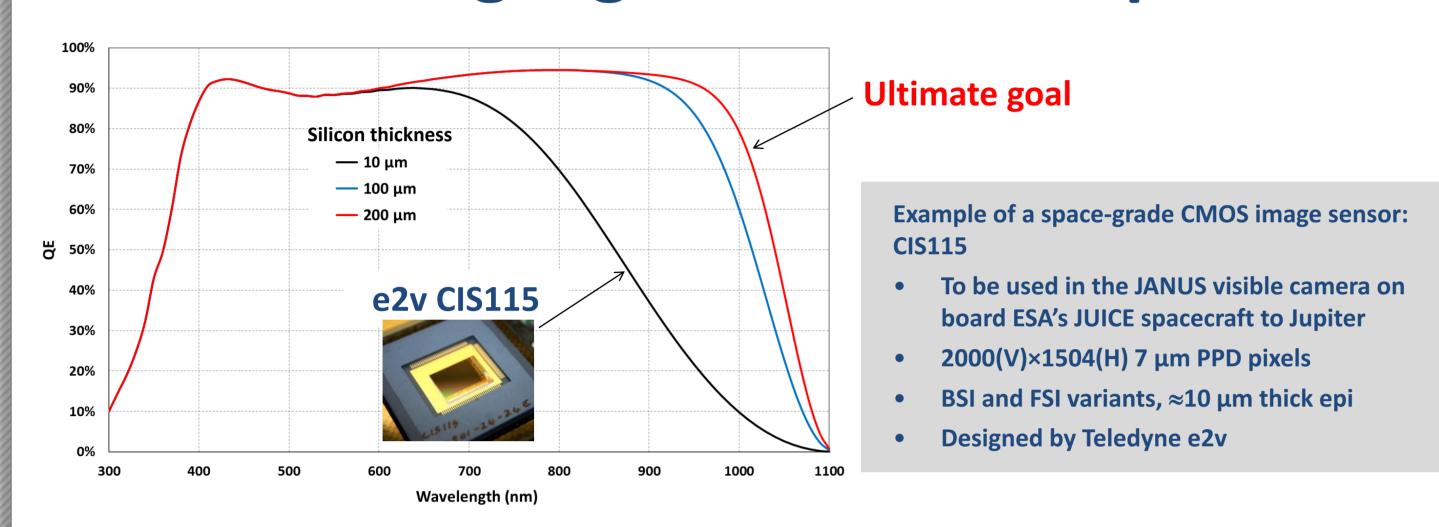

## Achieving high QE with PPD pixels

Pinned photodiode is the preferred photosensitive element in CMOS image sensors for science due to their low readout noise, low dark current and high CVF. However, the silicon thickness is usually <10  $\mu$ m, limiting the QE for near-IR and soft X-rays.

Reverse biasing a PPD pixel is a great way to deplete thick substrate silicon and achieve high QE with minimum MTF deterioration by charge diffusion.

Traditional BSI PPD pixels cannot be reverse biased due to the electrical conduction between the front side p-well and the backside contact via the substrate.

## The new design

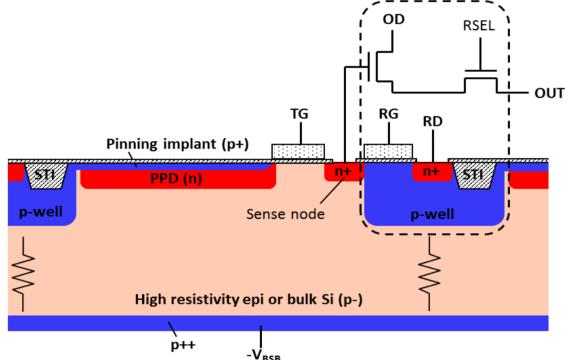

The new pixel design implements a deep, lightly doped n-type implant under the in-pixel p-wells. This implant, called "deep depletion extension" (DDE) is floating and does not connect to the PPDs.

In normal operation the DDE acquires its potential from the adjacent PPDs and becomes depleted. By choosing the appropriate doping profile and size of the DDE, its potential can be made lower than the pinning voltage, but still high enough to create a potential barrier. The DDE region acts as a bridge extending the depletions from the PPDs underneath the p-wells, creating a pinch-off and a potential barrier of sufficient height to prevent undesired substrate currents.

This design has a number of advantages:

- The excellent properties of the PPD are preserved, as it remains unchanged;

- The structure is compatible with any depleted thickness;

- Only one additional manufacturing step is required.

### The first prototype

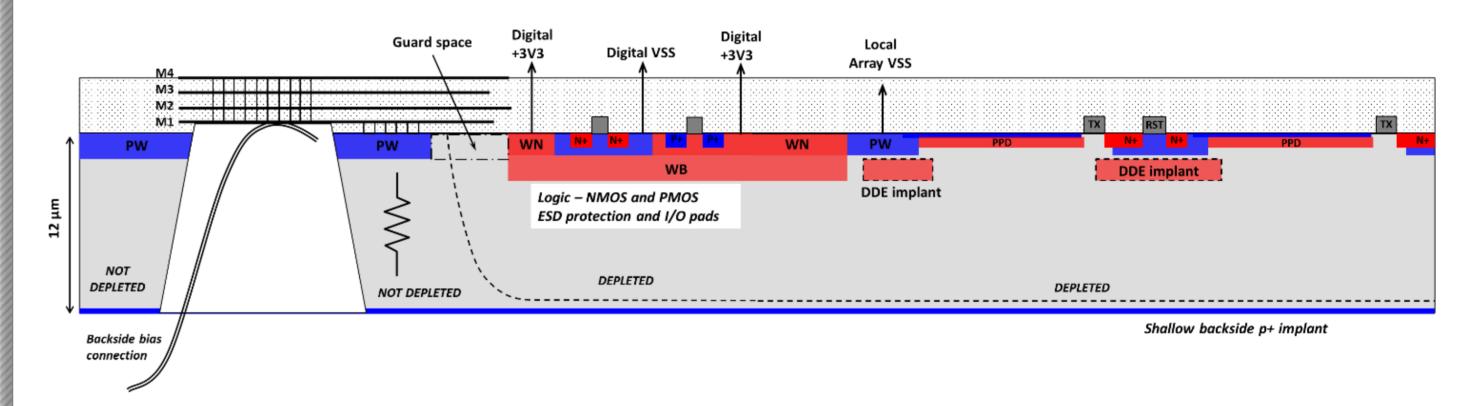

Using 180 nm CIS process from TowerJazz (with modifications) on 18  $\mu$ m epi for FSI chips; 10  $\mu$ m and 5.4  $\mu$ m pixel arrays implemented.

BSI variant (12 µm thick) using proprietary backthinning process from Teledyne e2v.

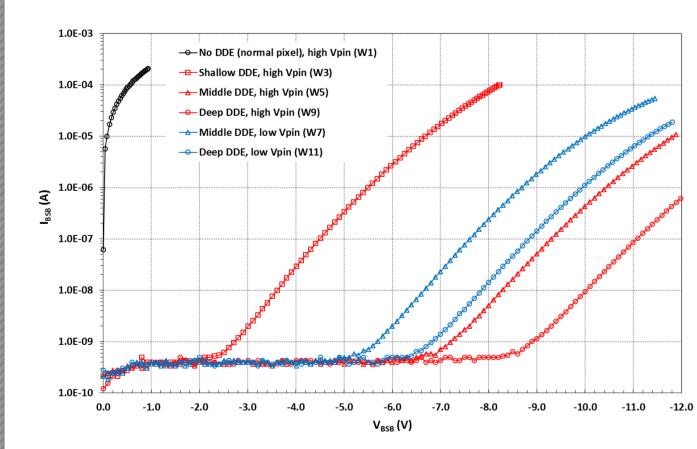

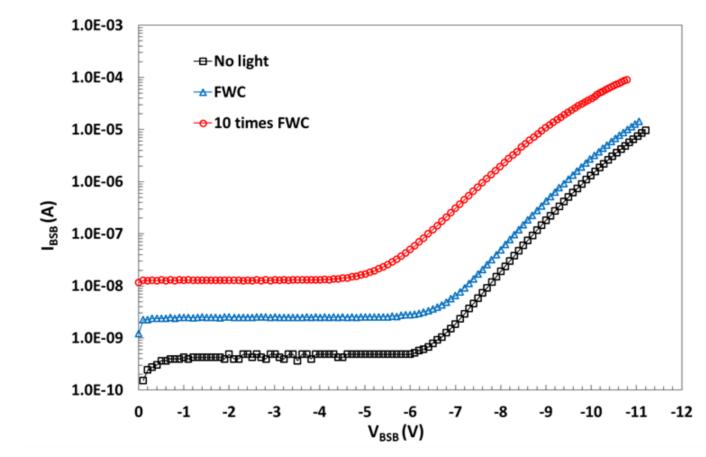

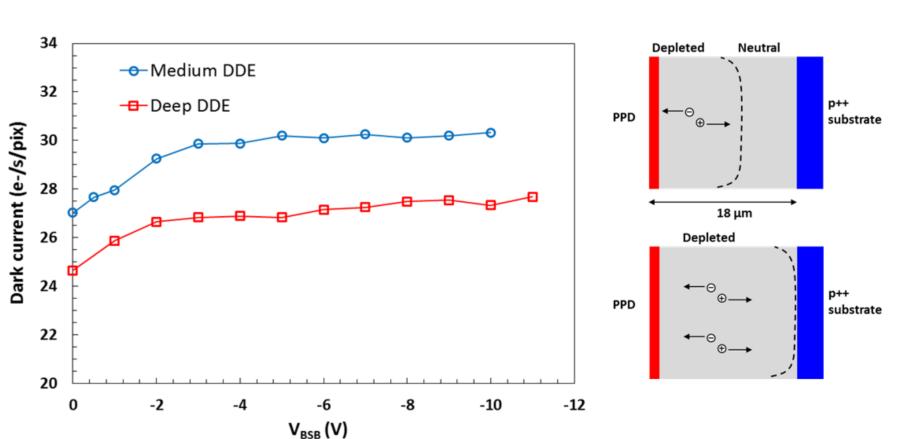

All chip variants can be reverse biased without significant leakage currents, and this is maintained under strong illumination (right). The leakage current mechanism is by thermionic emission of holes over the potential barrier. The onset of this is beyond full depletion, and the voltage threshold depends on the size and depth of the DDE as predicted by TCAD simulations.

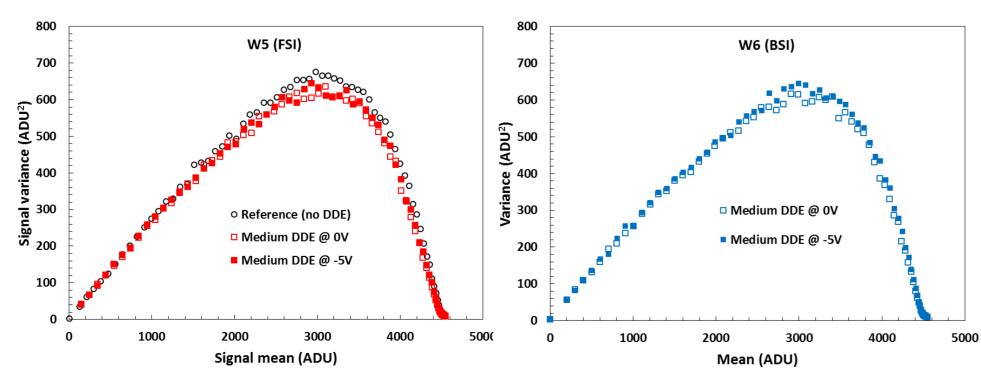

The photon transfer curves of the FSI and BSI variants are identical to the reference design.

## **Proving full depletion**

As the depletion increases in depth it reaches the backside interface with the p++ substrate and cannot increase anymore; at this point the bulk dark current is expected to level off. In FSI chips the data is consistent with the expectation of full depletion at -4V reverse bias.

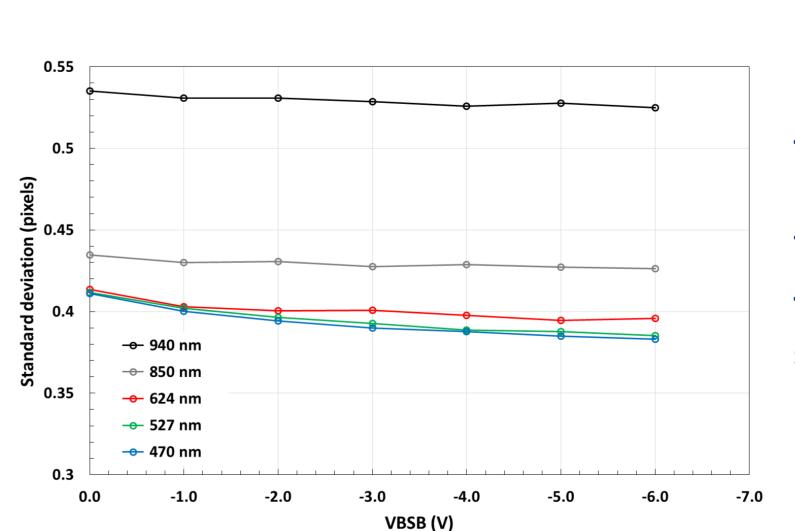

Spot pinhole illumination was used to investigate the depletion depth in BSI devices. Short wavelengths (for example 470 nm, 0.6  $\mu$ m absorption length in silicon) are absorbed near the backside, and if the depletion reaches the back of the device there will be less diffusion. Much longer wavelengths (for example 940 nm, 54  $\mu$ m absorption length) are absorbed throughout the thickness of the device and the charge spread is much less sensitive to the extent of depletion, in particular in our 12  $\mu$ m BSI devices.

The spot size dependence on the reverse bias for various wavelengths indicates that the device reaches full depletion.

The QE should be consistent with the silicon thickness.

**Reference:** Konstantin D. Stefanov, Andrew S. Clarke and Andrew D. Holland, "Fully Depleted Pinned Photodiode CMOS Image Sensor With Reverse Substrate Bias", IEEE Electron Device Letters, Vol. 38, No. 1, pp. 64-66 (2017).

Centre for Electronic Imaging

The Open University, Walton Hall, MK7 6AA

http://www.open.ac.uk/cei

Konstantin.Stefanov@open.ac.uk